仕様翻訳: The RISC-V Instruction Set Manual

Volume II: Privileged Architecture

Document Version 20211203

Editors: Andrew Waterman1, Krste Asanović1,2, John Hauser

1SiFive Inc.,

2CS Division, EECS Department, University of California, Berkeley

andrew@sifive.com, krste@berkeley.edu, jh.riscv@jhauser.us

December 4, 2021

本仕様書全バージョンの寄稿者 (アルファベット順): Krste Asanović, Peter Ashenden, Rimas Avižienis, Jacob Bachmeyer, Allen J. Baum, Jonathan Behrens, Paolo Bonzini, Ruslan Bukin, Christopher Celio, Chuanhua Chang, David Chisnall, Anthony Coulter, Palmer Dabbelt, Monte Dalrymple, Greg Favor, Dennis Ferguson, Marc Gauthier, Andy Glew, Gary Guo, Mike Frysinger, John Hauser, David Horner, Olof Johansson, David Kruckemyer, Yunsup Lee, Daniel Lustig, Andrew Lutomirski, Prashanth Mundkur, Jonathan Neuschäfer, Rishiyur Nikhil, Stefan O’Rear, Albert Ou, John Ousterhout, David Patterson, Dmitri Pavlov, Kade Phillips, Josh Scheid, Colin Schmidt, Michael Taylor, Wesley Terpstra, Matt Thomas, Tommy Thorn, Ray VanDeWalker, Megan Wachs, Steve Wallach, Andrew Waterman, Clifford Wolf, and Reinoud Zandijk.

この文書は Creative Commons Attribution 4.0 International License の下で公開されている。

この文書は次のライセンスの下でリリースされた the RISC-V privileged specification version 1.9.1 から派生したものである: © 2010–2017 Andrew Waterman, Yunsup Lee, Rimas Avižienis, David Patterson, Krste Asanović. Creative Commons Attribution 4.0 International License.

Table of Contents

- 導入

- 2 Control and Status Registers (CSRs)

- 3 Machine-Level ISA, Version 1.12

- 4 Supervisor-Level ISA, Version 1.12

- 5 "Svnapot" Standard Extension for NAPOT Translation Contiguity, Version 1.0

- 6 "Svpbmt" Standard Extension for Page-Based Memory Type, Version 1.0

- 7 "Svinval" Standard Extension for Fine-Grained Address-Translation Cache Invalidation, Version 1.0

- 8 Hypervisor Extension, Version 1.0

- 9 RISC-V Privileged Instruction Set Listings

- 10 History

- Bibliography

- 翻訳抄

導入

導入

この文書は RISC-V 特権アーキテクチャについて説明する。これは特権命令だけではなくオペレーティングシステムの実行や外部デバイスの接続に必要な追加命令など、非特権 ISA を超えた RISC-V システムのすべての側面をカバーする。

我々の設計上の決定に関する解説はこの段落のような形式になっており、読者が使用自体にしか興味がない場合は読み飛ばしてもかまわない。

このドキュメントで説明する特権レベルの設計全体は、非特権 ISA を変更することなく、場合によっては ABI さえも変更することなく、全く異なる特権レベルの設計に置き換えることができることを簡単に述べておく。特にこの特権仕様は既存の一般的なオペレーティングシステムを実行するように設計されているため従来のレベルベースの保護モデルを具現化している。他の特権仕様はより柔軟な他の保護ドメインモデルを具現化しているかもしれない。表現を簡単にするためにこの文章はこれが唯一の特権アーキテクチャであるかのように書かれている。

1.1 RISC-V 特権ソフトウェアスタック用語

1.1 RISC-V 特権ソフトウェアスタック用語

このセクションでは RISV-V で使用できる様々な特権ソフトウェアスタックのコンポーネントを説明するために使用する用語について説明する。

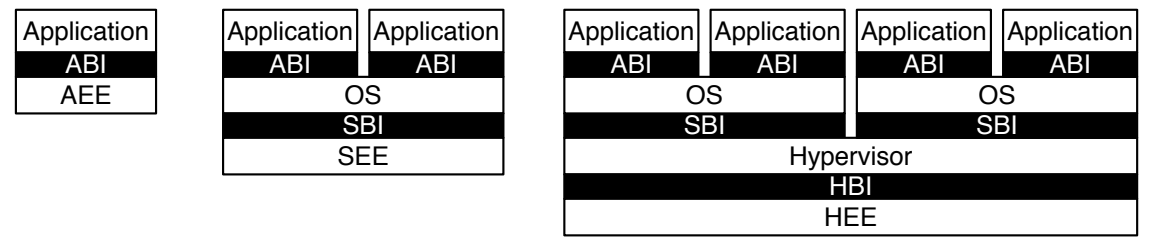

Figure 1.1 は RISC-V アーキテクチャでサポートできるソフトウェアスタックの一部を示している。左側はアプリケーション実行環境 (AEE) で実行される唯一のアプリケーションのみをサポートする単純なシステムを示している。このアプリケーションは特定のアプリケーションバイナリインターフェース (ABI) で実行するようにコード化されている。ABI には、サポートされるユーザレベル ISA と、AEE と対話するための一連の ABI 呼び出しが含まれている。ABI はアプリケーションから AEE の詳細を隠蔽し AEE の実装をより柔軟にする。同じ ABI を複数の異なるホスト OS 上でネイティブに実装することも、異なるネイティブ ISA を持つマシン上で動作するユーザモードエミュレーション環境でサポートすることもできる。

我々のグラフィカルな慣例では、抽象的なインターフェースを白い文字が付いたボックスで表現し、インターフェースを実装するコンポーネントの具体的なインスタンスから分離する。

中央の構成は複数のアプリケーションのマルチプログラム実行をサポートする従来のオペレーティングシステム (OS) を示している。各アプリケーションは ABI を介して OS と通信し OS は AEE を提供する。アプリケーションが ABI を介して AEE とインターフェースするのとと同様に、RISC-V オペレーティングシステムはスーパーバイザバイナリインターフェース (SBI) を介してスーパーバイザ実行環境 (SEE) とインターフェースする。SBI はユーザレベルおよびスーパーバイザレベルの ISA と SBI 関数コールのセットで構成される。すべての SEE 実装で単一の SBI を使用すると、単一の OS バイナリイメージを任意の SEE 上で実行することができる。SEE はローエンドハードウェアプラットフォームにおける単純なブートローダーと BIOS スタイルの IO システムであったり、ハイエンドサーバにおけるハイパーバイザ提供の仮想マシンであったり、またはアーキテクチャシミュレーション環境におけるホスト OS 上の薄い変換レイヤーであったりする。

ほとんどのスーパーバイザレベルの ISA 定義は SBI が実行環境やハードウェアプラットフォームから分離されておらず、仮想化や新しいハードウェアプラットフォームの導入が複雑になっている。

一番右の構成は複数のマルチプログラム OS が単体のハイパーバイザでサポートされている仮想マシンモニター構成を示している。各 OS は SBI を介して、SEE を提供するハイパーバイザと通信する。ハイパーバイザはハイパーバイザバイナリインターフェース (HBI) を使用してハイパーバイザ実行環境 (HEE) と通信し、ハイパーバイザをハードウェアプラットフォームの詳細から分離する。

ABI、SBI、HBI はまだ開発中だが、現在 SBI が S モード OS によって再帰的に提供されるタイプ 2 ハイパーバイザのサポートを優先している。

RISC-V ISA のハードウェア実装ではさまざまな実行環境 (AEE, SEE, HEE) をサポートするために一般に特権 ISA 以外の追加機能が必要になる。

1.2 特権レベル

1.2 特権レベル

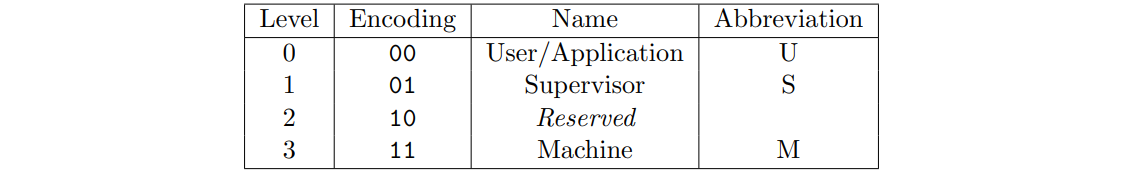

RISC-V ハードウェアスレッド (ハート; hart) は常に 1 つ以上の CSR (制御および状態レジスタ;control and state registers) にモードとしてエンコードされた特権レベルで実行されている。現在 Table 1.1 に示す 3 つの RISC-V 特権レベルが定義されている。

特権レベルはソフトウェアスタックの様々なコンポーネント間で保護を提供するために使用され、現在の特権モードで許可されていない操作を実行しようとすると例外が発生する。これらの例外は通常、、基礎となる実行環境へのトラップを引き起こす。

この説明ではコードが記述される特権レベルとコードが実行される特権レベルを分離するようにしているが、多くの場合この 2 つは結びついている。例えばスーパーバイザレベルのオペレーティングシステムは、3 つの特権モードを持つシステム上ではスーパーバイザモードで実行できるが、2 つ以上の特権モードを持つシステムでは古典的な仮想マシンモニタの下でユーザモードで実行することもできる。どちらの場合も同じスーパーバイザレベルのオペレーティングシステムバイナリコードを使用し、スーパーバイザレベルの SBI にコード化されているため、スーパーバイザレベルの特権レベルと CSR を使用することが期待される。ユーザモードでゲスト OS を実行する場合、すべてのスーパーバイザレベルの動作はより高い特権レベルで実行されている SEE によってトラップされエミュレートされます。

マシンレベルは最高の特権を持ち、RISC-V ハードウェアプラットフォームにとって唯一必須の特権レベルである。マシンモード (M-mode) で実行されるコードはマシンの実装に低レベルでアクセスできるため通常は本質的に信頼されている。M-mode は RISC-V 上でセキュアな実行環境を管理するためにしようできる。ユーザモード (U-mode) とスーパーバイザモード (S-mode) はそれぞれ通常のアプリケーションとオペレーティングシステムの使用を目的としている。

各特権レベルにはオプションの拡張やバリアントを備えた特権 ISA 拡張機能のコアセットがある。例えばマシンモードはメモリ保護のためにオプションの標準拡張機能をサポートしている。また第 8 章で説明されているようにスーパーバイザモードを拡張してタイプ 2 ハイパーバイザの実行をサポートすることもできる。

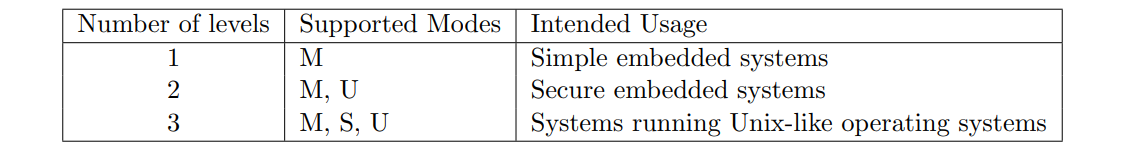

Table 1.2 に示すように、実装では分離性の低下と引き換えに実装コストを削減するために 1 つから 3 つの特権モードをすることができる。

M-mode はマシン全体に自由にアクセスできる唯一のモードであるため、すべてのハードウェア実装は M-mode を提供しなければならない。最も単純な RISC-V 実装では M-mode のみを提供することができるが、これでは不正なアプリケーションコードや悪意のあるアプリケーションコードに対する保護は提供されない。

オプションの PMP 機能のロック機能は M-mode しか実装されていない場合でも限定的な保護を提供することができる。

多くの RISC-V 実装ではシステムの残りの部分をアプリケーションコードから保護するために少なくともユーザモード (U-mode) もサパオートしている。スーパーバイザモード (S-mode) を追加することでスーパーバイザレベルのオペレーティングシステムと SEE を分離することができる。

ハートは通常、何らかのトラップ (スーパーバイザ呼び出しやタイマー割り込みなど) によってトラップハンドラへカーク換えが強制されるまでアプリケーションコードを U-mode で実行する。トラップハンドラは通常より特権的なモードで実行される。その後ハートはトラップハンドラを実行し、最終的には U-mode でトラップされた元の命令以降に実行を再開する。特権レベルを上げるトラップは垂直トラップと呼ばれ、同じ特権レベルに留まるトラップは水平トラップと呼ばれる。RISV-V 特権アーキテクチャは異なる特権レイヤーへのトラップの柔軟なルーティングを提供する。

水平トラップはより低い特権モードの水平トラップハンドラに制御を戻す垂直トラップとして実装できる。

1.3 デバッグモード

1.3 デバッグモード

実装にはオフチップデバッグ製造テストをサポートするデバッグモードも含まれる場合がある。デバッグモード (D-mode) は M モードよりもさらに多くのアクセス権を備えた追加の特権モードと考えることができる。別のデバッグしよう提案ではデバッグモードでの RISC-V ハートの動作について説明している。デバッグモードでは D-mode でのみアクセス可能ないくつかの CSR アドレスが予約sレ、プラットフォームの物理アドレス空間の一部を予約することもできる。

2 Control and Status Registers (CSRs)

2 Control and Status Registers (CSRs)

3 Machine-Level ISA, Version 1.12

3 Machine-Level ISA, Version 1.12

4 Supervisor-Level ISA, Version 1.12

4 Supervisor-Level ISA, Version 1.12

5 "Svnapot" Standard Extension for NAPOT Translation Contiguity, Version 1.0

5 "Svnapot" Standard Extension for NAPOT Translation Contiguity, Version 1.0

6 "Svpbmt" Standard Extension for Page-Based Memory Type, Version 1.0

6 "Svpbmt" Standard Extension for Page-Based Memory Type, Version 1.0

7 "Svinval" Standard Extension for Fine-Grained Address-Translation Cache Invalidation, Version 1.0

7 "Svinval" Standard Extension for Fine-Grained Address-Translation Cache Invalidation, Version 1.0

8 Hypervisor Extension, Version 1.0

8 Hypervisor Extension, Version 1.0

9 RISC-V Privileged Instruction Set Listings

9 RISC-V Privileged Instruction Set Listings

10 History

10 History

Bibliography

Bibliography

- Robert P. Goldberg. Survey of virtual machine research. Computer, 7(6):34–45, June 1974.

- Juan Navarro, Sitaram Iyer, Peter Druschel, and Alan Cox. Practical, transparent operating system support for superpages. SIGOPS Oper. Syst. Rev., 36(SI):89–104, December 2002.

翻訳抄

RISC-V 特権 ISA に関する 2021 年の仕様書。

- “ The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Document Version 20211203”, Editors Andrew Waterman, Krste Asanović, and John Hauser, RISC-V International, December 2021.